CD4051B, CD4052B, CD4053B SCHS047K - AUGUST 1998 - REVISED MARCH 2023

# CD405xB CMOS Single 8-Channel Analog Multiplexer or Demultiplexer With Logic-Level Conversion

## 1 Features

Texas

INSTRUMENTS

- Wide range of digital and analog signal levels: Digital: 3 V to 20 V

- Analog: ≤ 20 V<sub>P-P</sub>

- Low ON resistance, 125  $\Omega$  (typical) over 15 V<sub>P-P</sub> signal input range for  $V_{DD} - V_{EE} = 18 \text{ V}$

- High OFF resistance, channel leakage of  $\pm 100 \text{ pA}$  (typical) at V<sub>DD</sub> – V<sub>EE</sub> = 18 V

- Logic-level conversion for digital addressing signals of 3 V to 20 V ( $V_{DD} - V_{SS}$  = 3 V to 20 V) to switch analog signals to 20  $V_{P-P}$  ( $V_{DD} - V_{FF}$ = 20 V) matched switch characteristics,  $r_{ON}$  = 5  $\Omega$ (typical) for  $V_{DD} - V_{EE}$  = 15 V very low quiescent power dissipation under all digital-control input and supply conditions, 0.2 µW (typical) at  $V_{DD} - V_{SS} = V_{DD} - V_{EE} = 10 V$

- Binary address decoding on chip

- 5 V, 10 V, and 15 V parametric ratings •

- 100% tested for guiescent current at 20 V

- Maximum input current of 1 µA at 18 V over full package temperature range, 100 nA at 18 V and 25°C

- Break-before-make switching eliminates channel overlap

## 2 Applications

- Analog and digital multiplexing and demultiplexing

- Analog to digital and digital to analog conversion

- Signal gating

- **Factory automation**

- **Televisions**

- **Appliances**

- **Consumer audio**

- Programmable logic circuits

- Sensors

## **3 Description**

The CD405xB analog multiplexers and demultiplexers are digitally-controlled analog switches having low ON impedance and very low OFF leakage current. These multiplexer circuits dissipate extremely low quiescent power over the full  $V_{DD} - V_{SS}$  and  $V_{DD} - V_{FF}$  supplyvoltage ranges, independent of the logic state of the control signals.

| Package Information <sup>(1)</sup> |         |        |  |  |

|------------------------------------|---------|--------|--|--|

| IBER                               | PACKAGE | BODY S |  |  |

| PART NUMBER | PACKAGE        | BODY SIZE (NOM)    |

|-------------|----------------|--------------------|

|             | J (CDIP, 16)   | 19.50 mm × 6.92 mm |

|             | N (PDIP, 16)   | 19.30 mm × 6.35 mm |

| CD405xB     | D (SOIC, 16)   | 9.90 mm × 3.91 mm  |

|             | NS (SOP, 16)   | 10.30 mm × 5.30 mm |

|             | PW (TSSOP, 16) | 5.00 mm × 4.40 mm  |

(1) For all available packages, see the orderable addendum at the end of the data sheet.

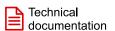

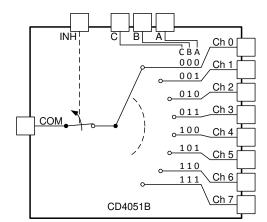

#### Functional Diagrams of CD405xB

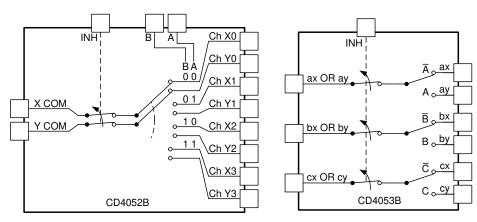

### **5** Pin Configuration and Functions

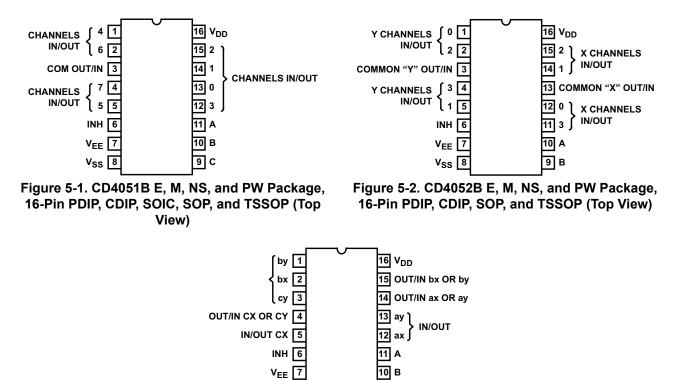

#### Figure 5-3. CD4053B E, M, NS, and PW Package, 16-Pin PDIP, CDIP, SOP, and TSSOP (Top View)

V<sub>SS</sub> 8

9 C

Table 5-1. Pin Functions CD4051B

| PIN |                 |      | DESCRIPTION                           |

|-----|-----------------|------|---------------------------------------|

| NO. | NAME            | ITPE | DESCRIPTION                           |

| 1   | CH 4 IN/OUT     | I/O  | Channel 4 in/out                      |

| 2   | CH 6 IN/OUT     | I/O  | Channel 6 in/out                      |

| 3   | COM OUT/IN      | I/O  | Common out/in                         |

| 4   | CH 7 IN/OUT     | I/O  | Channel 7 in/out                      |

| 5   | CH 5 IN/OUT     | I/O  | Channel 5 in/out                      |

| 6   | INH             | I    | Disables all channels. See Table 8-1. |

| 7   | V <sub>EE</sub> |      | Negative power input                  |

| 8   | V <sub>SS</sub> |      | Ground                                |

| 9   | С               | I    | Channel select C. See Table 8-1.      |

| 10  | В               | I    | Channel select B. See Table 8-1.      |

| 11  | A               | I    | Channel select A. See Table 8-1.      |

| 12  | CH 3 IN/OUT     | I/O  | Channel 3 in/out                      |

| 13  | CH 0 IN/OUT     | I/O  | Channel 0 in/out                      |

| 14  | CH 1 IN/OUT     | I/O  | Channel 1 in/out                      |

| 15  | CH 2 IN/OUT     | I/O  | Channel 2 in/out                      |

| 16  | V <sub>DD</sub> | —    | Positive power input                  |

(1) I = input, O = output